yangbo

(HKZY_YangBo)

1

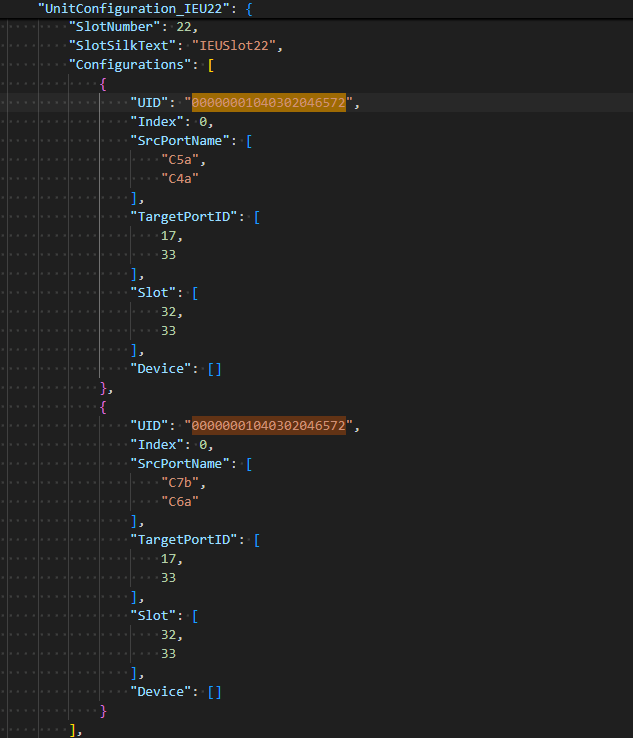

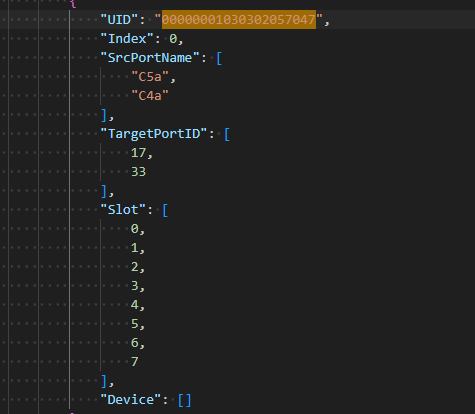

C5a和C4a有两种线缆接线方式:

接Riser后接GPU:

接硬盘背板:

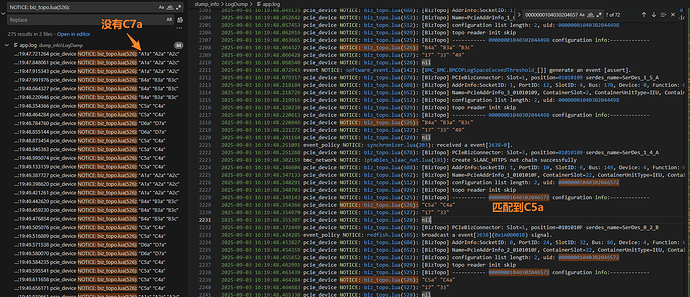

当前机型接线方式为下面的方式(cable_info日志):

从app.log的biz_topo.lua的匹配打印看,匹配日志看到00000001040302046572(接GPU的Riser卡)匹配到了 C5a和C4a,没有匹配到预期的C7b和C6b。

从而导致给到BIOS的丝印文件的RootPortDeviceID的偏移到了硬盘背板那边去,与实际匹配出现差异导致GPU卡未正常识别。

通过删除00000001040302046572(接GPU的Riser卡)的 C5a和C4a,GPU卡正常识别显示到BMC界面。

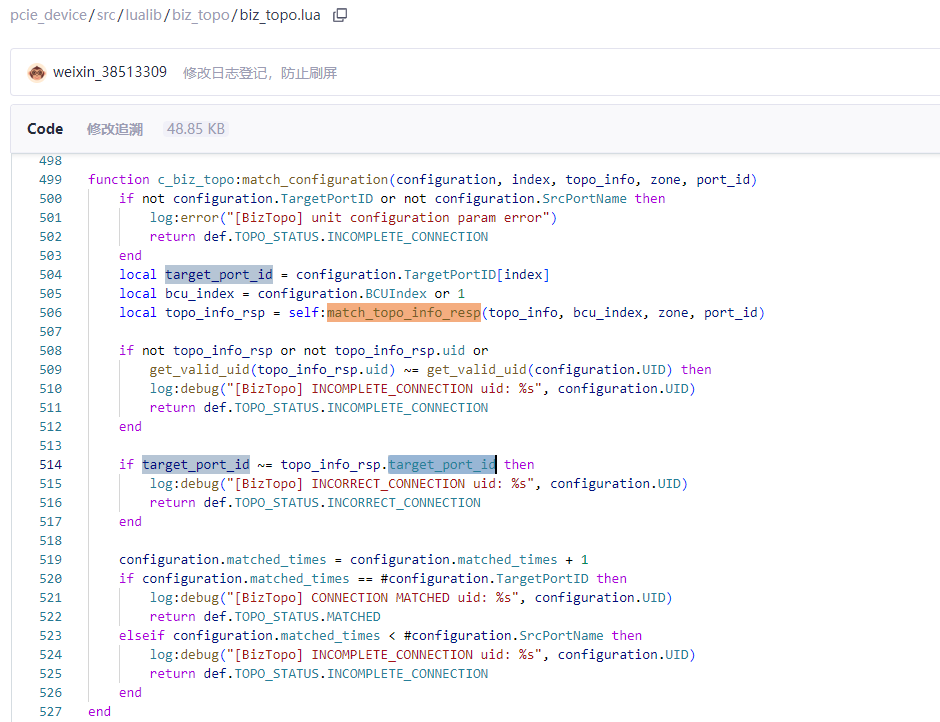

从pcie_device组件看匹配逻辑,是匹配的端口,这里没有匹配UID:

疑问:

1、这种要支持两种接线方式的,除了配置2个PSR来规避,是否会考虑匹配逻辑上添加逻辑判断?

2、这种是否有可以借鉴的检测方法,提前识别这种可能得冲突?

另一个关于PSR的类似问题:【PSR】有4个同一UID的UnitConfiguration配置,出现概率性匹配到不同的配置 - #4,来自 DDDDang_p8ere

补充:

该问题是基于5.5分支的BMC版本。

您好,方便发一下一键收集日志到这个邮箱huangding12@huawei.com吗?现在想看看能不能通过匹配SrcPortName来解决,想详细看看问题。

zybwh

(张雨博)

4

C7b不应该接Riser把?鲲鹏硬件那边给的方案吗?

zybwh

(张雨博)

5

还有,一个UniConfiguration只能有一种匹配的连线,

你要是两种连法,应该创建两个UnitConfiguration

还有,可以在UT里面把实际环境的数据打桩模拟一下,然后利用vscode的debug模式可以一步一步看具体发生了什么,方便debug

可以参考这个用例:https://gitcode.com/openUBMC/pcie_device/blob/main/test/unit/biz_topo/test_topo_monitor.lua#L298

ocy

(wuzhou-ouchangyun)

6

博哥,关于这里我有个问题请教一下,两种连法创建两个UnitConfiguration,那么对应SlotNumber属性是一个逻辑值,而不是实际物理值吗?同时Configurations下的Index是依据BCU的CPLD返回去决定吗?

zybwh

(张雨博)

7

unitconfiguration的slot会作为这个riser的槽位,包括展示啊什么的都会用

所以理论上在一个环境上不应该有两个实体riser有同样的槽位号

因此在连线设计的时候需要考虑, 是否需要支持这么多种插法?而且从硬件、bmc角度来说,也不是所有场景都能覆盖全。

比如说,我有两个一模一样的型号riser,对应21,22,然后21插c5a c4a,22插c7b,c6b。听上去好像没什么难度,但实际上我看连线的时候就会发现,c5a c4a c6b c7b都插了同一个riser,还缺一个方法来区分这两个riser。

SMC设计的时候是保留了一个index号,用来区分同uid riser不同实例,但这个对bcu的smc和riser的smc要求很高,尤其是riser自己得知道自己是哪个。

所以你看配的时候很多index是0,就是硬件自己也不知道自己是哪个。

回到他这里的这种配法,意思应该是,Riser21在xx场景下,接c5a c4a,在另一种发货场景下,接c6b和c7b (c5a c4a接了其他的硬件)

那么如果需要支持两种的话,应该是:UnitConfiguration 21 (6572接c5a c4a)然后再有一个UnitConfiguration22(6572接c7b c6b)

总之来说,我个人觉得,宁愿维护多种PSR,也不要一个PSR里面配多个,因为会导致线缆配置和检测逻辑很复杂。

zybwh

(张雨博)

9

这里 6572不是接的D5a D4b么,是不是配错了

yangbo

(HKZY_YangBo)

10

是的,目前另一个问题也是通过区分PSR来处理的。因为出现过一次发货的时候,因缺少某些物料,又希望环境能够跑起来,所以出现了PSR覆盖了多种场景的诉求。