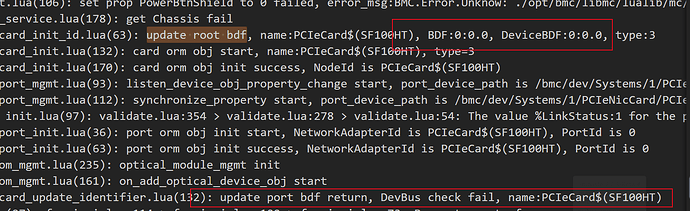

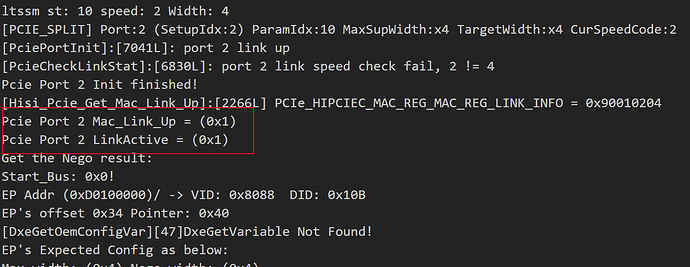

额,这个portid和Serdes有啥对应关系的吗?,我看我收集到的日志中,这个bdf信息是有问题的,这里会影响这个网卡的NCSI功能不

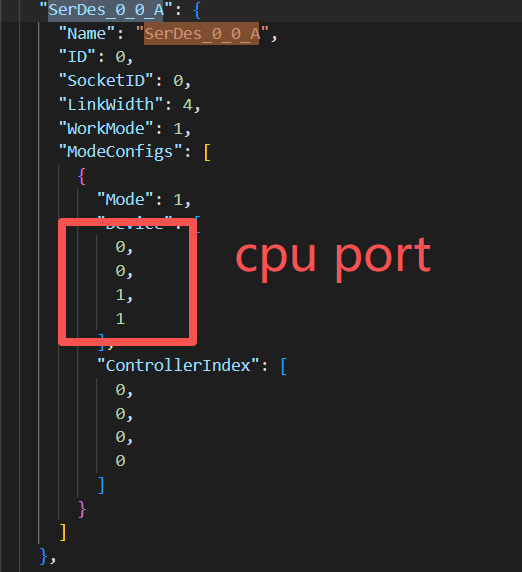

BCU中配置如下:

“SerDes_0_5”: {

“Name”: “SerDes_0_5”,

“ID”: 5,

“SocketID”: 0,

“LinkWidth”: 8,

“WorkMode”: 1,

“ModeConfigs”: [

{

“Mode”: 1,

“Device”: [

0,

0,

0,

0,

2,

2,

2,

2

],

“ControllerIndex”: [

0,

0,

0,

0,

0,

0,

0,

0

]

}

]

},

“BusinessConnector_1”: {

“Name”: “Down_1”,

“Direction”: “Downstream”,

“Slot”: 1,

“LinkWidth”: “X4”,

“MaxLinkRate”: “PCIe 4.0”,

“ConnectorType”: “PCIe CEM”,

“UpstreamResources”: [

{

“Name”: “SerDes_0_5”,

“ID”: 0,

“Offset”: 0,

“Width”: 4

}

],

“RefPCIeAddrInfo”: “#/PcieAddrInfo_M2_1”

},

“BusinessConnector_2”: {

“Name”: “Down_2”,

“Direction”: “Downstream”,

“Slot”: 2,

“LinkWidth”: “X4”,

“MaxLinkRate”: “PCIe 2.0”,

“ConnectorType”: “PCIe CEM”,

“UpstreamResources”: [

{

“Name”: “SerDes_0_5”,

“ID”: 1,

“Offset”: 4,

“Width”: 4

}

],

“RefMgmtConnector”: “#/Connector_NIC_1”,

“RefPCIeAddrInfo”: “#/PcieAddrInfo_NIC_1”

},

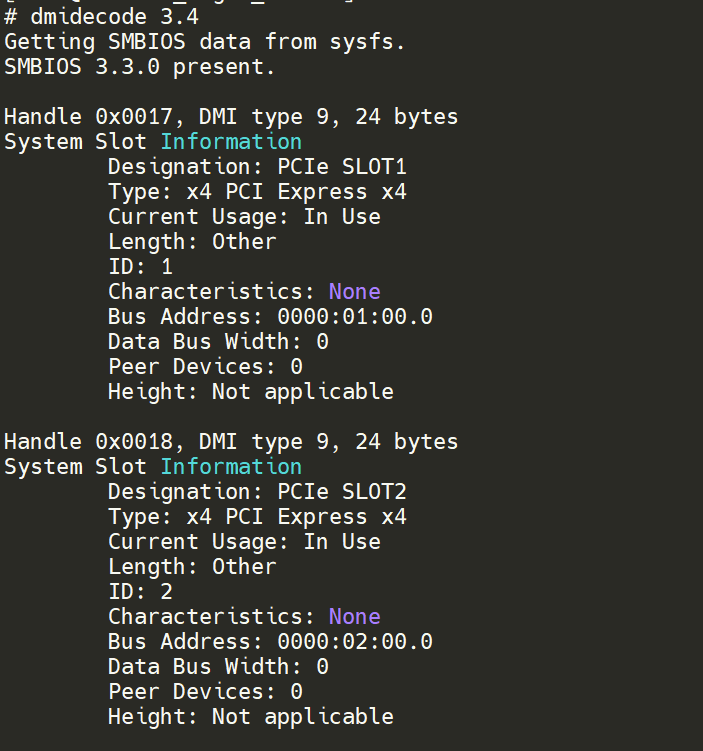

“PcieAddrInfo_NIC_1”: {

“Segment”: 0,

“GroupID”: 1,

“SocketID”: 0,

“SlotID”: 2,

“PortID”: 2,

“Bus”: 2,

“Device”: 0,

“Function”: 0,

“Location”: “BCU”,

“ComponentType”: 8,

“ContainerSlot”: “${Slot}”,

“ContainerUID”: “00000001020302071127”,

“ContainerUnitType”: “BCU”,

“GroupPosition”: “PcieAddrInfo_NIC_1_${GroupPosition}”

},

能否帮忙看下是哪块的配置有问题吗?