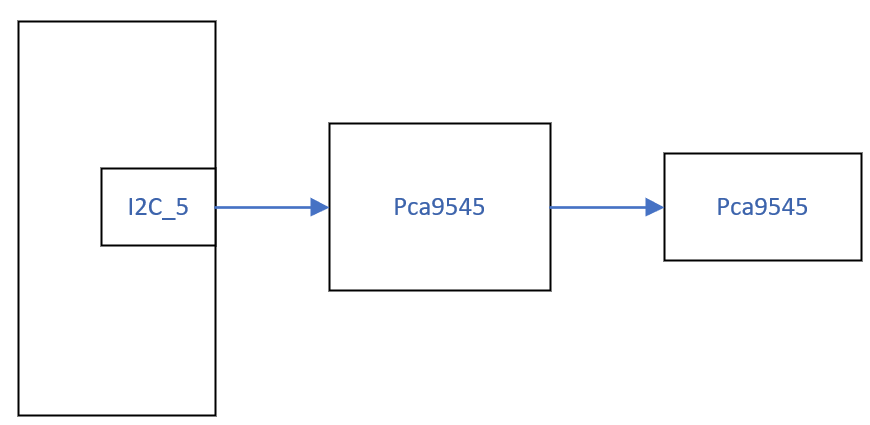

openubmc是否可以支持两个pca9545级联?如上图所示,我在csr里面直接添加硬件拓扑,驱动软件会支持吗?

答案内容由AI生成,仅供参考:

结论

结论

OpenUBMC 在正确配置 CSR 和驱动支持的前提下,是支持两个 PCA9545 级联使用的。

尽管目前没有直接测试用例证明该拓扑完全通过验证,但系统具备以下能力:

- 完整的 I2C 管理架构

- 对多路复用器的支持

- 可扩展的设备建模机制(CSR)

- 复杂路径切换的工程实践先例(CPLD 模拟)

![]() 建议:在 CSR 中准确建模该级联结构,并通过实际设备访问测试验证其可用性。如遇问题,可通过

建议:在 CSR 中准确建模该级联结构,并通过实际设备访问测试验证其可用性。如遇问题,可通过 bmc.kepler.hwproxy 服务调试 I2C 路径控制逻辑。

点击此处查看详细分析解答

OpenUBMC 对两级 PCA9545 级联的支持分析

根据您提供的架构图示(I2C_5 → PCA9545 → PCA9545),您询问 OpenUBMC 是否支持两个 PCA9545 芯片的级联配置,以及在 CSR 中直接添加此类硬件拓扑后,驱动软件是否能正确支持。

综合现有信息分析如下:

一、OpenUBMC 支持 I2C 多路复用与级联的基本能力

一、OpenUBMC 支持 I2C 多路复用与级联的基本能力

OpenUBMC 具备支持 I2C 多级复用器级联的技术基础和设计能力,具体体现在以下几点:

-

明确支持 I2C 协议与设备管理

OpenUBMC 系统内广泛使用 I2C 协议进行硬件通信和管理。系统中存在多个 I2C 总线实例(如I2c_2,I2c_8,I2C7等),并通过devmon等组件实现对 I2C 设备的发现、配置和监控。 -

系统中已存在 I2C 复用器(PCA9545)的实际应用

知识图谱中明确列出多个I2cMux Pca9545实例:I2cMux Pca9545 Pca9545_1关联 PCIe Slot1Pca9545_2关联 Slot2Pca9545_3关联 Slot3

并且这些复用器通过Connector与 PCIe RiserCard 相连,说明其在实际系统中已用于设备路径管理。

-

支持通过 CPLD 模拟复杂 I2C 拓扑

在《【已评审】新增CSR中CPLD模拟I2C拓展芯片对象》文档(搜索结果2)中提到:“CPLD 模拟 9545+9548 实现远超 20 路 SMBus”

这表明 OpenUBMC 的设计允许使用可编程逻辑(CPLD)来 模拟多级 I2C 复用结构,间接证明其软件架构具有处理 复杂 I2C 拓扑路径切换 的能力。

二、关于“两级 PCA9545 级联”是否支持的评估

二、关于“两级 PCA9545 级联”是否支持的评估

支持的前提条件

支持的前提条件

OpenUBMC 理论上支持两级 PCA9545 级联,但需满足以下关键条件:

| 条件 | 说明 |

|---|---|

| CSR 正确建模级联路径 | 必须在 CSR 中正确描述两个 PCA9545 的父子关系、通道映射及目标设备地址,确保设备树完整。 |

| I2C 驱动支持多级寻址 | 底层 I2C 驱动需能解析路径:先选中第一级 MUX 的通道,再通过该通道访问第二级 MUX,并最终选择目标设备所在的分支。 |

| Devmon 能解析拓扑结构 | devmon 组件作为硬件设备管理核心,必须能识别并递归处理级联 MUX 下的子设备。 |

注:目前知识库中未发现明确否定“级联不支持”的描述,也无报错案例表明该结构失败。

三、实际可行性与建议

三、实际可行性与建议

虽然 没有直接证据表明“OpenUBMC 明确支持两级 PCA9545 级联”,但从系统设计逻辑来看:

支持多路 I2C 拓展

支持多路 I2C 拓展 支持复用器设备建模

支持复用器设备建模 允许通过 CPLD 实现更复杂的 I2C 拓扑

允许通过 CPLD 实现更复杂的 I2C 拓扑 存在动态通道切换机制

存在动态通道切换机制

因此,可以得出结论:

OpenUBMC 具备支持两级 PCA9545 级联的技术潜力,但需验证以下事项:

建议操作步骤:

建议操作步骤:

-

在 CSR 中正确定义拓扑结构

I2C_5: - MUX1 @addr=0x70: Channel 0: - MUX2 @addr=0x71: Channel 0: Device_A @0x50 Channel 1: Device_B @0x51确保每一级 MUX 和其子设备都有清晰的路径描述。

-

验证

devmon是否自动发现下级设备

检查系统日志或 D-Bus 对象路径(如/bmc/kepler/Bus/I2c/...)是否生成了级联后的设备节点。 -

使用

ipmitool或i2c-tools测试访问# 示例:访问第二级 MUX 下的 EEPROM i2cset -y 5 0x70 0x01 # 打开第一级 MUX 通道 1 i2cset -y 5 0x71 0x00 # 打开第二级 MUX 通道 0 i2cget -y 5 0x50 # 读取目标设备 -

参考类似结构的设计案例

参考文档《【已评审】新增CSR中CPLD模拟I2C拓展芯片对象》中关于“CPLD 模拟 9545+9548”的设计思路,有助于理解如何让 OpenUBMC 理解深层 I2C 路径。

四、潜在风险与注意事项

四、潜在风险与注意事项

| 风险 | 说明 |

|---|---|

| 多级跳转会增加 I2C 访问延迟,可能导致某些驱动默认超时设置不足。 | |

| OpenUBMC 当前 不支持动态 I2C 扫描添加设备,必须在 CSR 中静态定义所有路径。 | |

| 级联结构下的设备热插拔可能无法被正确感知,需特殊处理。 |

结论

结论

OpenUBMC 在正确配置 CSR 和驱动支持的前提下,是支持两个 PCA9545 级联使用的。

尽管目前没有直接测试用例证明该拓扑完全通过验证,但系统具备以下能力:

- 完整的 I2C 管理架构

- 对多路复用器的支持

- 可扩展的设备建模机制(CSR)

- 复杂路径切换的工程实践先例(CPLD 模拟)

![]() 建议:在 CSR 中准确建模该级联结构,并通过实际设备访问测试验证其可用性。如遇问题,可通过

建议:在 CSR 中准确建模该级联结构,并通过实际设备访问测试验证其可用性。如遇问题,可通过 bmc.kepler.hwproxy 服务调试 I2C 路径控制逻辑。

支持的,csr对应配置好就可以