问题描述

硬盘背板在线升级cpld,在升级进度95%的时候出现失败

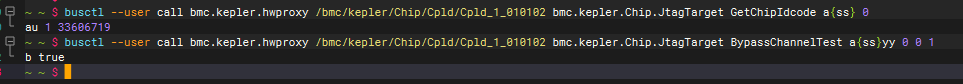

1、 通过GetChipIdcode可以成功获取Id为0x0200CC3F

2、 BypassChannelTest 返回成功

3、 升级Cpld时失败了,Linux kernel log 报错 verify TDO [5] expect:0xfe, sample:0x0,随后 svf execute error(0x15)。

请问有什么排查方向

dump_info/RTOSDump/sysinfo/journalctl.log

2026-03-19T02:44:08.733419+0000 2102315QRVD9RC100007 kernel: [I2C-11-RT<-5|-5>] M<0x4e|0x1|0x0|1|10> L<1|2|0> C<1|0|2> E<0x801|0x0|0x0|0x1> I<0x0|0x710|0x0>

2026-03-19T02:44:11.203438+0000 2102315QRVD9RC100007 kernel: [I2C-03-RT<-5|-5>] M<0x71|0x0|0x0|3|10> L<1|0|0> C<1|0|0> E<0x1|0x0|0x0|0x1> I<0x0|0x710|0x0>

2026-03-19T02:44:11.223419+0000 2102315QRVD9RC100007 kernel: [I2C-03-RT<-5|-5>] M<0x71|0x0|0x0|3|10> L<1|0|0> C<1|0|0> E<0x1|0x0|0x0|0x1> I<0x0|0x710|0x0>

2026-03-19T02:44:39.822975+0000 2102315QRVD9RC100007 systemd[1]: dev-shm-firmware_mgmt-cgroup.mount: Deactivated successfully.

2026-03-19T02:45:08.223410+0000 2102315QRVD9RC100007 kernel: [I2C-08-RT<-5|-5>] M<0x47|0x1|0x0|1|10> L<1|1|0> C<1|0|1> E<0x801|0x0|0x0|0x1> I<0x0|0x510|0x0>

2026-03-19T02:45:08.623446+0000 2102315QRVD9RC100007 kernel: [I2C-08-RT<-5|-5>] M<0x21|0x1|0x0|1|10> L<1|1|0> C<1|0|1> E<0x801|0x0|0x0|0x1> I<0x0|0x710|0x0>

2026-03-19T02:45:08.823448+0000 2102315QRVD9RC100007 kernel: [I2C-11-RT<-5|-5>] M<0x4e|0x1|0x0|1|10> L<1|2|0> C<1|0|2> E<0x801|0x0|0x0|0x1> I<0x0|0x710|0x0>

2026-03-19T02:45:54.969758+0000 2102315QRVD9RC100007 kernel: 60,2026-03-19 02:45:54,5049,svf_sr_verify_tdo,1432,verify TDO [5] expect:0xfe, mask: 0xfe, sample:0x0

2026-03-19T02:45:54.970489+0000 2102315QRVD9RC100007 kernel: 61,2026-03-19 02:45:54,5049,svf_scan_register,1487,[SVF] scan register verify tdo, recv_len:262

2026-03-19T02:45:54.970845+0000 2102315QRVD9RC100007 kernel: 62,2026-03-19 02:45:54,5049,svf_do_scan_register,1555,[SVF] scan register err:0x15

2026-03-19T02:45:54.990455+0000 2102315QRVD9RC100007 kernel: 63,2026-03-19 02:45:54,5049,cpld_jtag_svf_exec,1727,svf execute error(0x15), line 5034 pos 917220 keyword 254 word(;)

2026-03-19T02:45:54.990964+0000 2102315QRVD9RC100007 kernel: 64,2026-03-19 02:45:54,5049,cpld_jtag_load_logic,151, svf exec failed(0x15)

2026-03-19T02:45:55.007304+0000 2102315QRVD9RC100007 kernel: 65,2026-03-19 02:45:54,5049,cpld_process,937,cpld std load failed(21)!

2026-03-19T02:46:08.293460+0000 2102315QRVD9RC100007 kernel: [I2C-08-RT<-5|-5>] M<0x47|0x1|0x0|1|10> L<1|1|0> C<1|0|1> E<0x801|0x0|0x0|0x1> I<0x0|0x710|0x0>

2026-03-19T02:46:08.693419+0000 2102315QRVD9RC100007 kernel: [I2C-08-RT<-5|-5>] M<0x21|0x1|0x0|1|10> L<1|1|0> C<1|0|1> E<0x801|0x0|0x0|0x1> I<0x0|0x710|0x0>

2026-03-19T02:46:08.853418+0000 2102315QRVD9RC100007 kernel: [I2C-11-RT<-5|-5>] M<0x4e|0x1|0x0|1|10> L<1|2|0> C<1|0|2> E<0x801|0x0|0x0|0x1> I<0x0|0x710|0x0>

2026-03-19T02:47:08.483429+0000 2102315QRVD9RC100007 kernel: [I2C-08-RT<-5|-5>] M<0x47|0x1|0x0|1|10> L<1|1|0> C<1|0|1> E<0x801|0x0|0x0|0x1> I<0x0|0x710|0x0>

2026-03-19T02:47:08.883418+0000 2102315QRVD9RC100007 kernel: [I2C-08-RT<-5|-5>] M<0x21|0x1|0x0|1|10> L<1|1|0> C<1|0|1> E<0x801|0x0|0x0|0x1> I<0x0|0x710|0x0>

2026-03-19T02:47:08.974825+0000 2102315QRVD9RC100007 kernel: [I2C-11-RT<-5|-5>] M<0x4e|0x1|0x0|1|10> L<1|2|0> C<1|0|2> E<0x801|0x0|0x0|0x1> I<0x0|0x710|0x0>