基于2509的openUBMC

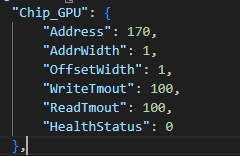

在csr中配置了如下芯片:

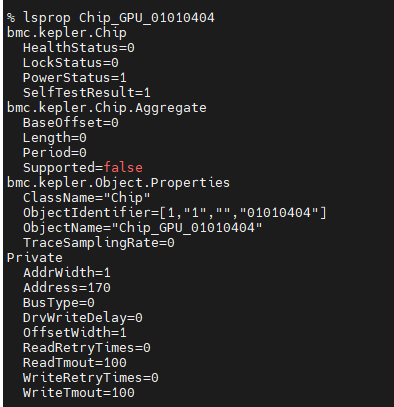

BMC正常加载了该芯片:

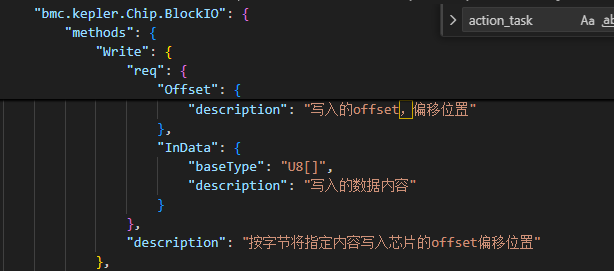

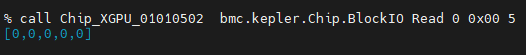

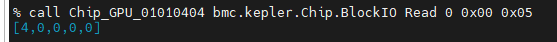

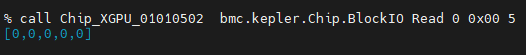

使用bmc.kepler.Chip.BlockIO Read/Write进行调试,发送如下命令:

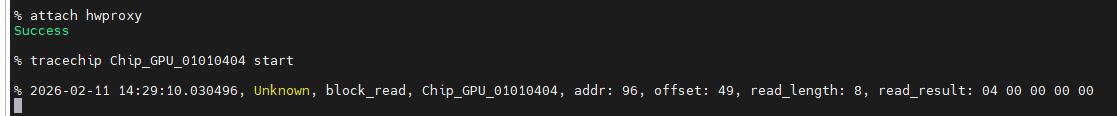

同时通过attach hwproxy,tracechip Chip_GPU_01010404 start查看芯片访问实时打印,发现打印如下:

为何chip_GPU配置的地址为170,但是打印里的地址为96; 命令里发的偏移是0x00,但是打印里的offset为49;命令里的读取长度为0x05,打印里的读取长度为8?

没有 是我截图的问题,这两个对象我都有尝试,截图截乱了,已改正

器件拓扑:I2C2 → I2C_mux_9545 → SMC_forward → chip_GPU

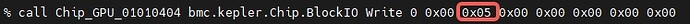

请问这个write_data怎么解析,实际写入chip的数据是什么?

这个应该是smc forward的数据,BMC读写经过smc的器件其实不会直接写给chip,而是通过smc转发的,这个是把数据封装为smc格式发给smc了,你看看smc的地址是不是96

是的 SMC地址是96。

目前想知道的是write_data应该怎么解析,红框中的数据是实际写入chip的吧?

对应的写命令是:

也就是inData的第一个字节不会写入么?

第一个字节是对应的data的长度,不在数据里,或者说这个其实是参数的一个要求,数组类型的先写数组长度,后面n个值才是数组的实际数据

wbf

(Wbf)

10

我这边配gpu读出来全是0,跟预期不符,这个你是怎么调试的呢?

![]()